メインページ/Electronics/AVR/pushpull1

提供:MwWiki

目次[非表示] |

[編集] プッシュプル・トランス式 DC-ACコンバータ

その1

参考資料: パワーMOSFET活用の基礎と実際 (CQ出版社)

FET2個とセンタータップ付きトランスを使用した DC-ACコンバーターを作成します。AC出力は100Vです。

なぜトランス使用かというと

- 直接 H ブリッジで140V以上の高電圧をスイッチするのが怖い

- アーム回路が1個で済む

- トランス容量を小さなものから試していけば、問題があって大電流が流れてデバイス類が損傷する確率が減る

というのが理由です。

しかし、トランスをFETスイッチする場合、インダクタンスに対して電流をオフしたときに発生するサージ電圧(リンギング)が発生するため、スナバと呼ばれる除去回路を使ってFETを保護する必要があります。

スナバ回路は C と R を直列に構成するもので、発生するリンギングの周波数を計測してCRの値を決める必要があるとのことです。以下のサイトが詳しいです。

http://www.maximintegrated.com/en/app-notes/index.mvp/id/3835

[編集] FET の基礎

順番が前後しますが、MOSFETの基本的な動作確認からしてみます。以下のページを参考にしながら、FETによるスイッチの勉強。

http://www.geocities.jp/zattouka/GarageHouse/micon/circuit/FET.htm

ちなみにPLCの世界では、ローサイド・スイッチ、ハイサイド・スイッチのことを、シンク、ソースと呼ぶようです。

http://www.orientalmotor.co.jp/tech/teruyo/vol35/

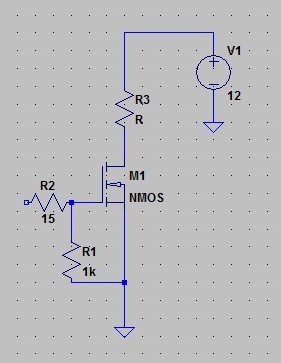

まずは以下の回路です。

M1: IRFU3410

FETを使い慣れていないので、足を確認するのがいつも面倒。特にIRのデータシートは足に小さく123と書いてるが、正面なのかどうかもよくわからない。

R3: 負荷抵抗 50Ω

V1: 12V

R1 はゲート入力が何も無いときにゲートが 0V になるようにプルダウンする抵抗です。事実、このR1 が無いと、R2 に何も入力していなくても、FETがON(R3 に電流が流れる) になったりならなかったりで不安定です。

R1無しだと何もゲートにつないでいなくても電流が流れてしまう

R1無しだと何もゲートにつないでいなくても電流が流れてしまう

さて、R2 に何ボルト入力すればONになるのか?

実験ではおよそ 1.3V あたりから電流が流れ始め、2.0Vぐらいでフルに流れました。データシートによれば、Vgsは Min 1.0V Max 2.0Vなので、大体合っています。

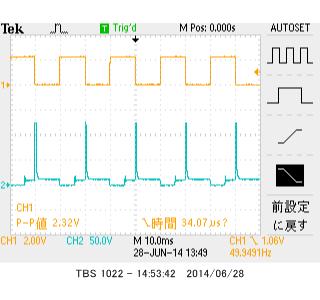

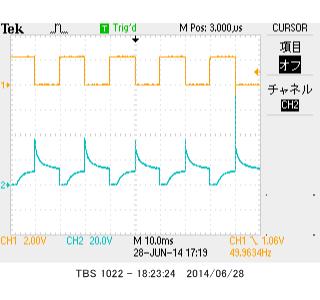

[編集] 方形波入力

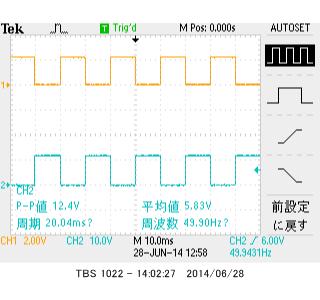

次に R2 入力にオーディオジェネレータを接続して、方形波を入力してみます。私の使っている LEADER LAG-120B は出力抵抗 600Ωなので、R2 の手前に 560Ωを並列に入れました。周波数は 50Hz です。入力電圧は先ほどの実験から、2V ちょっとが良うさそうなので、そのあたりにしています。

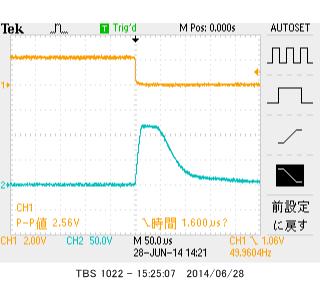

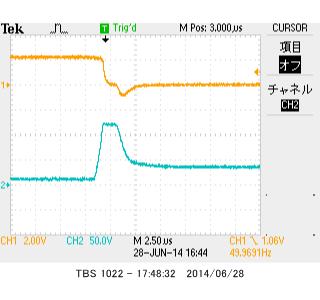

期待通りの出力になりました。立ち上がりと立ち下がりを見てみます。

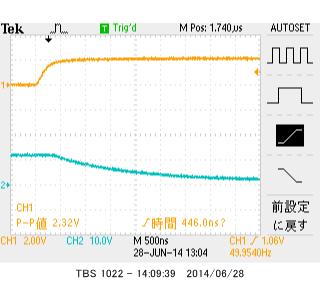

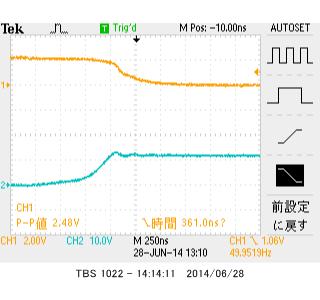

立ち上がり(左) 立ち下がり(右)

立ち上がりはもっさりしています。立ち下がりは波形が歪んでいますが、立ち上がりよりは早いようです。

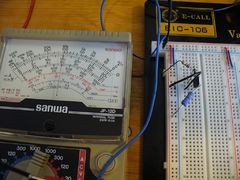

電流値は、FET ON 時に 200mA 程度ですが、この方形波を与えた場合は 100mA の指示となりました。デューティ比 50% ですから半分の電流値というこになりました。

周波数を変えた場合、50Hz から周波数を上げていくと、5kHz ぐらいまででは電流値は変わりません。50kHz では80mA、500kHz では15mA 程度となります。これはスイッチ回数が多くなるほどスイッチングロスが増えるためです。世の中的には 20kHz が上限、というのがこの結果からも理解できます。

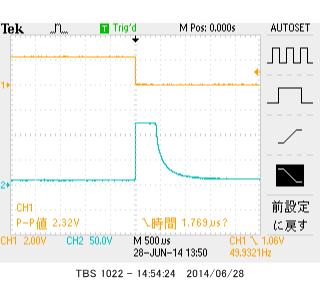

[編集] 負荷をトランスにした場合

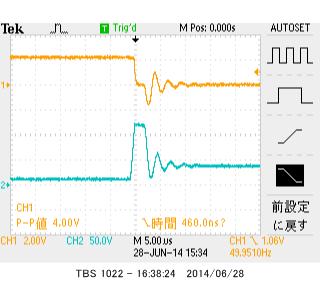

負荷をトランスにして発生するリンギングを見てみます。

使用トランス

電源電圧は 12V。

左のように、100V を超えるサージ電圧が発生しています。このサージ部分を拡大したのが右です。

このページの Fig.3 のような、発振しながら減衰する波形を期待したのですが、そういうものは出ていません。

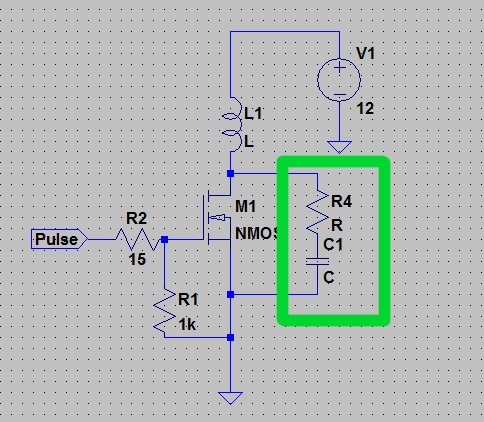

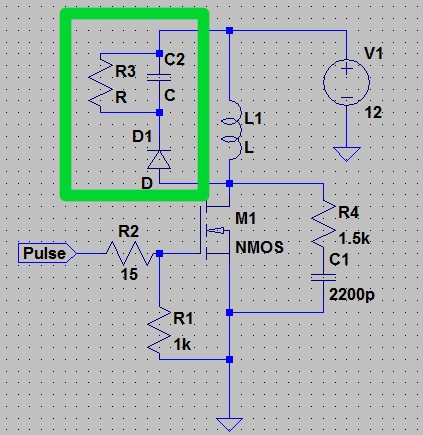

とりあえず、当てずっぽうで、R4=200Ω、C1=3900pF を付けてみました。回路は以下になります。

(左)取り付け前 (右)取り付け後

取り付けると、かえってサージのおさまりが悪くなってしまいました。

ここで試しに負荷(トランス2次側)に電球を付けてみました。そして波形を見てみると。。

リンギングは無負荷のときに発生する、とどこかの本に書いてあった気がするのですが、そうではなかった。。

では、ここからスナバ回路の値を決めて、リンギングを減衰できるかやってみます。

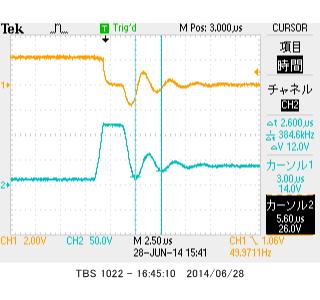

1) まず、適当な値のCをFETの D-S 間に入れてみる。maxim integrated のページでは 35MHz という高い周波数に対して 330pF にしているので、ここではそれより大きな 1000pF にしてみる。

2) 周波数は 167kHz ぐらいになりました。

maxim integrated の説明の

"adjust the value of this capacitor until the frequency of the spike resonance is reduced by a factor of two. The value of this resulting capacitor will be three times the value of the parasitic capacitance that is creating the voltage spikes. "

の部分、つまり、周波数が1/2になるCの値の1/3が寄生容量になるらしいですが、なぜそうなるかよくわかりません。ともあれ、1000pF は大きすぎたので 800pF ぐらいを試したいところですが、そんな手持ちはありません。とりあえずここでは 800pF で半分の周波数 192kHz になったと想定して、その 1/3 のコンデンサ 260pF ぐらいを付けるとします。

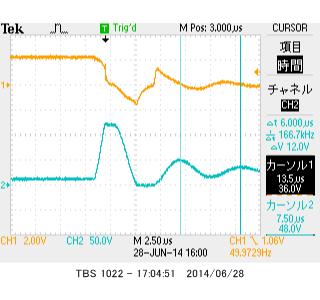

3) 値の計算

寄生インダクタンス

Parasitic inductance = L = 1 / [(2 x 3.14 x 385kHz)² * 260pF] = 0.658mH

寄生インピーダンス

Characteristic impedance = Z = SQRT (0.658mH / 260pF) = 1.59x10^3

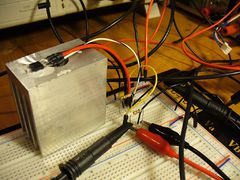

したがって、R=1.5kΩ、また "C should be between four and ten times the parasitic capacitance of 260pF" より、2200pF (8.4倍) の値で試してみます。

CRを追加した回路。FETは熱くなるので放熱器にテープで仮止め。このMOSFETの難点はネジ止めできないこと。

CRを追加した回路。FETは熱くなるので放熱器にテープで仮止め。このMOSFETの難点はネジ止めできないこと。

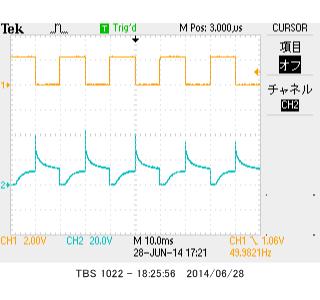

OK。しかし無負荷時のスパイク状のサージは無くなっていない。。

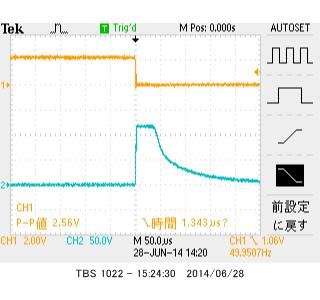

[編集] CRD スナバ回路

ここでもう一度、「パワーMOSFET活用の基礎と実際」の p125 を見ると、スナバ回路とは別に CRD(クランプ)回路なるものがあります。スナバ回路の説明はありますが、CRD回路の説明はありません。サンケンのパワーIC STR5A100D の資料にCRDスナバ回路の説明があり、この回路によってサージとリンギングの両方を抑えることができると書いてあります。17ページに回路定数も載っているので、これを参考に CRD スナバを造ります。ここでは、スナバ回路は既に定数も判明しているので、サージだけを抑えるCRD回路を追加します。

サンケンの資料では、D は汎用品、R3=470kΩ、C2=1000pF です。一方、「パワーMOSFET」本では R3=51k、C2=0.1μFで、かなり開きがあります。とりあえず本の値で試します。

(左)CRDなし (右)CRDあり

CRDなしの場合、右端の波形のようにサージが頻発していましたが、CRDを付けたところ、それはなくなりました。無負荷のときは相変わらず大きなサージが出ます。これは少しばかり負荷電流を流しておくということになるのだろうか?

パワーMOSFET 本 p145 にその答えはありました。それは「負荷オープン検出回路を付ける」でした。つまり、無負荷状態で発生してしまうような大きなサージ電圧を防ぐための常用的な回路は無いということです。

(このページは書きかけです。。)